Digital television terrestrial broadcast coding orthogonal frequency division multiplexing COFDM transmission system occupies a very important position in the research of HDTV due to its strong anti-multipath interference performance and easy realization of mobile reception. The encoding and decoding technology in COFDM system is an important factor that affects the performance of the system. This article is based on the idea of ​​a maximum likelihood decoding-Viterbi VB decoding algorithm, from the perspective of FPGA implementation to discuss the decoding of inner code (shrink convolutional code) in COFDM system.

1 Brief description of design algorithm

In the HDTV terrestrial broadcast COFDM system, the inner code used is a punctured convolutional code. In addition to the 1/2 main code rate, there are also convolutional codes with 2/3, 3/4, 5/6, and 7/8 code rates. In the actual transmission channel, the noise is generally additive white Gaussian noise (AWGN), and the binary signal sequence is input to the AWGN channel. In order to make full use of the information of the channel output signal and improve the reliability of the transmission system decoding, the channel output signal is first quantized, and the Q level quantization sequence is input to the Viterbi decoder. Therefore, the VB decoding algorithm used in this paper is a soft decision translation Code algorithm.

1.1 Convolutional code encoding of main code rate 1/2

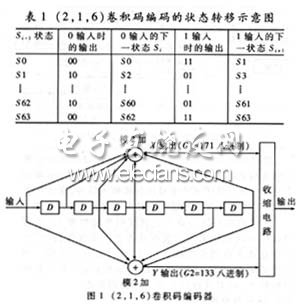

At present, in international satellite communications and many communication systems, (2, 1, 6) codes are the preferred standard convolutional codes using VB decoding. Because the code can minimize the bit error rate and overcome the phase error, in the HDTV terrestrial broadcast COFDM transmission system, the inner code uses (2, 1, 6) code, and its sub generator is (171, 133) , Are octal. The corresponding generator polynomial GD = 1 + D + D2 + D3 + D6 1 + D2 + D3 + D5 + D6 df = 10. The block diagram of its encoder is shown in Figure 1.

Since the (2, 1, 6) code has 64 states, for the sake of intuition, it uses a list method to express its fence diagram, as shown in Table 1.

1.2 Implementation of shrinking convolutional codes

In order to realize multi-code rate transmission, without increasing the complexity of the decoder when the code rate is increased, in this design, (2, 1, 6) codes are subjected to signal augmentation and puncturing (Puncctured). As shown in Fig. 1, after the above encoding, the specific position in the output codeword is deleted. In this way, convolutional codes with higher code rates of 2/3, 3/4, 5/6, and 7/8 can be generated.

1.3 Brief description of Viterbi decoding algorithm

Viterbi VB decoding algorithm is a maximum likelihood decoding algorithm. In the decoding process at the receiving end, it is divided into hard-decision and soft-decision decoding according to the different processing methods of the received symbols. Under the same decoding algorithm, although hard-decision decoding is simpler and easier to implement than soft-decision decoding, it loses 2 to 3 dB in performance. Therefore, the FPGA implementation of this article is based on soft decision. The specific algorithm is as follows:

(1) Starting from a certain time unit j = m, calculate the partial path metric for all partial paths of length j branch entering each state. For each state of 64 states, select and store a partial path with the largest metric and a partial metric value as the reserved path.

(2) j increases by 1, and all branch metrics that enter each state at this time are added to the metrics of the alternative path at the previous moment connected to these branches to obtain the alternative path that enters each state at this time, and store And delete all other paths.

(3) In order to achieve a higher clock speed in FPGA design, this paper takes out the first piece of information elements of all 64 path registers when judging and outputting the information of the path register, and outputs the first piece of information according to the criterion of large number decision yuan.

2 FPGA implementation of Viterbi decoding

This article is in the Quartus circuit simulation environment launched by Altera, using the combination of AHDL language and schematic simulation to complete the FPGA implementation of the VB decoder.

2.1 The overall implementation of the decoder

The overall scheme of the decoder is shown in Figure 2.

The data at the origin is transmitted over the channel. After synchronization and channel estimation, the data is Viterbi quantized according to the CSI information, and the quantized information is deinterleaved and sent to the Viterbi decoding unit.

After receiving the front-end codeword, you must first fill in specific false symbols in the deleted position of the sender. This function is performed by the Depuncture unit. And the measurement calculation prohibition pulse is generated by the unit and sent to the main decoder, so that the decoder prohibits the measurement calculation of these symbols during decoding.

The decoding output of the main decoder is sent to the bit error rate monitoring unit, which determines whether the data is synchronously received through the statistics of the bit error rate, and at the same time sends the information to the self-synchronous monitoring unit for adjusting synchronization. When the entire decoding system is synchronized, a synchronization flag will be output, indicating that the system has been synchronized, and the synchronization state is maintained by the synchronization unit.

2.2 Implementation of decoder sub-module

2.2.1 Viterbi decoding module with R = 1/2

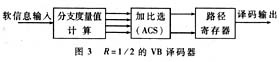

According to the above VB algorithm, for a soft decision decoder, it should have the following parts:

(1) Metric value register: used to store the metric value of each path. The pre-stage should also have a state generator that generates 64 states and branch values.

(2) Accumulator, comparator and decision device. It is used to accumulate soft distances respectively, compare the size of each path metric and select the value of the output information element.

(3) Path register: used to store the surviving path.

The module design is shown in Figure 3.

The branch metric value calculation part first calculates the metric value of each branch according to the received soft decision information, and the metric value calculation cannot be performed at the position where the Depuncture module outputs the prohibit pulse. The result is sent to the add-compare selection circuit. The output of each state transition obtained from Table 1 accumulates the branch metric, and the comparison and selection circuit is used to obtain the reserved path. When the path metrics of the 64 states in the path register are equal, the decoding information is output through the large number decision circuit and sent to the lower-level error monitoring and self-synchronization circuit.

This new 0 cycle iPhone 4 Battery to replace your faulty,defective,cracked,blister,leaking,jump percent battery,only fits for iPhone 4 not for other models. New IPhone 4 Battery Replacement cycle life time about 500 times, after 300 times still can keep 80% capacity. We are preofessional supply for IPhone Battery with 0 Cycle. We offer 12 months warranty,every piece of battery have passed CE,RoHS,MSDS and UN38.3 certification.

IPhone 4 Battery Pack

Nominal voltage: 3.7V

Limited charge voltage: 4.2V

Capacity:1420mAh (5.2whr)

Cell size: 42x32x82mm

iPhone 4 Battery

IPhone 4 Battery,IPhone 4 Battery Replacement,jump percent battery,IPhone Battery with 0 Cycle

Shenzhen Aokal Technology Co., Ltd. , https://www.aokal.com